DS05-10187-3E

# **MEMORY**

# CMOS 1M × 16 BIT FAST PAGE MODE DYNAMIC RAM

# MB8118160A-60/-70

#### CMOS 1,048,576 × 16 BIT Fast Page Mode Dynamic RAM

#### ■ DESCRIPTION

The Fujitsu MB8118160A is a fully decoded CMOS Dynamic RAM (DRAM) that contains 16,777,216 memory cells accessible in 16-bit increments. The MB8118160A features a "fast page" mode of operation whereby high-speed random access of up to  $1,024 \times 16$  bits of data within the same row can be selected. The MB8118160A DRAM is ideally suited for mainframe, buffers, hand-held computers video imaging equipment, and other memory applications where very low power dissipation and high bandwidth are basic requirements of the design. Since the standby current of the MB8118160A is very small, the device can be used as a non-volatile memory in equipment that uses batteries for primary and/or auxiliary power.

The MB8118160A is fabricated using silicon gate CMOS and Fujitsu's advanced four-layer polysilicon and two-layer aluminum process. This process, coupled with advanced stacked capacitor memory cells, reduces the possibility of soft errors and extends the time interval between memory refreshes. Clock timing requirements for the MB8118160A are not critical and all inputs are TTL compatible.

#### ■ PRODUCT LINE & FEATURES

| Parar                    | neter             | MB8118160A-60              | MB8118160A-70          |

|--------------------------|-------------------|----------------------------|------------------------|

| RAS Access Time          |                   | 60 ns max.                 | 70 ns max.             |

| Random Cycle Time        |                   | 110 ns min.                | 130 ns min.            |

| Address Access Time      |                   | 30 ns max.                 | 35 ns max.             |

| CAS Access Time          |                   | 15 ns max.                 | 17 ns max.             |

| Fast Page Mode Cycle Tin | ne                | 40 ns min.                 | 45 ns min.             |

| Low Power Dissipation    | Operating current | 880 mW max.                | 825 mW max.            |

| Low Power Dissipation    | Standby current   | 11 mW max. (LTTL level)/5. | 5 mW max. (CMOS level) |

- 1,048,576 words × 16 bit organization

- Silicon gate, CMOS, Advanced Stacked Capacitor Cell

- All input and output are TTL compatible

- 1,024 refresh cycles every 16.4 ms

- Self refresh function

- Early write or OE controlled write capability

- RAS-only, CAS-before-RAS, or Hidden Refresh

- Fast page mode, Read-Modify-Write capability

- On chip substrate bias generator for high performance

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

#### ■ ABSOLUTE MAXIMUM RATINGS (See WARNING)

| Parameter                             | Symbol         | Value        | Unit |

|---------------------------------------|----------------|--------------|------|

| Voltage at any pin relative to Vss    | VIN, VOUT      | -0.5 to +7.0 | V    |

| Voltage of Vcc supply relative to Vss | Vcc            | -0.5 to +7.0 | V    |

| Power Dissipation                     | P <sub>D</sub> | 1.0          | W    |

| Short Circuit Output Current          | _              | 50           | mA   |

| Operating Temperature                 | Торе           | 0 to 70      | °C   |

| Storage Temperature                   | Тѕтс           | -55 to +125  | °C   |

**WARNING:** Permanent device damage may occur if the above **Absolute Maximum Ratings** are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **■ PACKAGE**

#### **Package and Ordering Information**

- 42-pin plastic (400 mil) SOJ, order as MB8118160A-xxPJ

- 50-pin plastic (400 mil) TSOP-II with normal bend leads, order as MB8118160A-xxPFTN

#### **■ CAPACITANCE**

$(T_A = 25^{\circ}C, f = 1 \text{ MHz})$

|                                            |                  | (1   | A = 20 0, 1 = 1 WIT 12) |

|--------------------------------------------|------------------|------|-------------------------|

| Parameter                                  | Symbol           | Max. | Unit                    |

| Input Capacitance, Ao toAo                 | C <sub>IN1</sub> | 5    | pF                      |

| Input Capacitance, RAS, LCAS, UCAS, WE, OE | C <sub>IN2</sub> | 5    | pF                      |

| Input/Output Capacitance, DQ1 to DQ16      | CDQ              | 7    | pF                      |

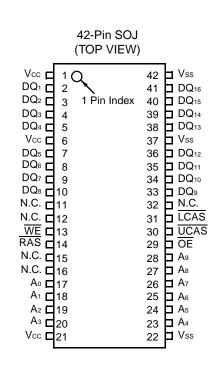

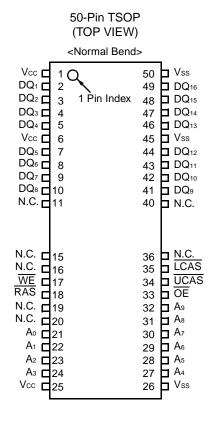

#### ■ PIN ASSIGNMENTS AND DESCRIPTIONS

| Designator                          | Function                                                                                                                                |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> to A <sub>9</sub>    | Address inputs row: A <sub>0</sub> to A <sub>9</sub> column: A <sub>0</sub> to A <sub>9</sub> refresh: A <sub>0</sub> to A <sub>9</sub> |

| RAS                                 | Row address strobe                                                                                                                      |

| LCAS                                | Lower column address strobe                                                                                                             |

| UCAS                                | Upper column address strobe                                                                                                             |

| WE                                  | Write enable                                                                                                                            |

| ŌĒ                                  | Output enable                                                                                                                           |

| DQ <sub>1</sub> to DQ <sub>16</sub> | Data Input/Output                                                                                                                       |

| Vcc                                 | +5.0 volt power supply                                                                                                                  |

| Vss                                 | Circuit ground                                                                                                                          |

| N.C.                                | No connection                                                                                                                           |

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                      | Notes | Symbol | Min. | Тур. | Max. | Unit | Ambient Operating Temp. |

|--------------------------------|-------|--------|------|------|------|------|-------------------------|

| Supply Voltage                 | 4     | Vcc    | 4.5  | 5.0  | 5.5  | V    |                         |

| Supply vollage                 | 1     | Vss    | 0.0  | 0.0  | 0.0  | V    |                         |

| Input High Voltage, all inputs | 1     | ViH    | 2.4  | _    | 6.5  | V    | 0°C to +70°C            |

| Input Low Voltage, all inputs* | 1     | VIL    | -0.3 | _    | 0.8  | V    |                         |

<sup>\*:</sup> Undershoots of up to -2.0 volts with a pulse width not exceeding 20 ns are acceptable.

#### **■ FUNCTIONAL OPERATION**

#### **ADDRESS INPUTS**

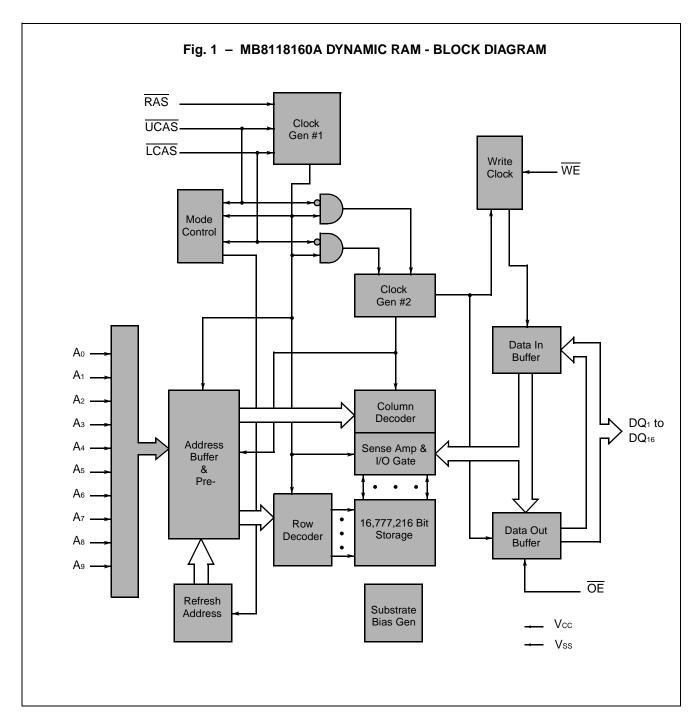

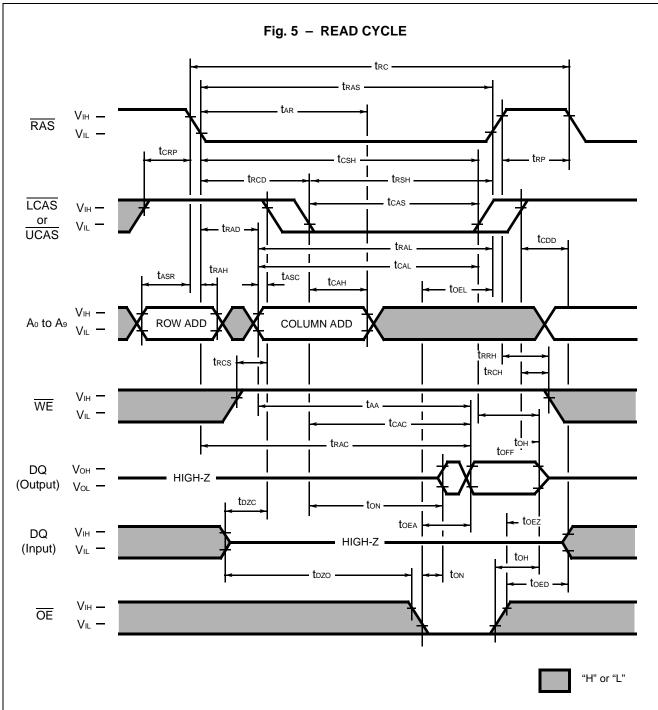

Twenty input bits are required to decode any sixteen of 16,777,216 cell addresses in the memory matrix. Since only twelve address bits ( $A_0$  to  $A_9$ ) are available, the column and row inputs are separately strobed by  $\overline{LCAS}$  or  $\overline{UCAS}$  and  $\overline{RAS}$  as shown in Figure 1. First, ten row address bits are input on pins  $A_0$ -through- $A_9$  and latched with the row address strobe ( $\overline{RAS}$ ) then, ten column address bits are input and latched with the column address strobe ( $\overline{LCAS}$  or  $\overline{UCAS}$ ). Both row and column addresses must be stable on or before the falling edges of  $\overline{RAS}$  and  $\overline{LCAS}$  or  $\overline{UCAS}$ , respectively. The address latches are of the flow-through type; thus, address information appearing after transfer (min.) + tr is automatically treated as the column address.

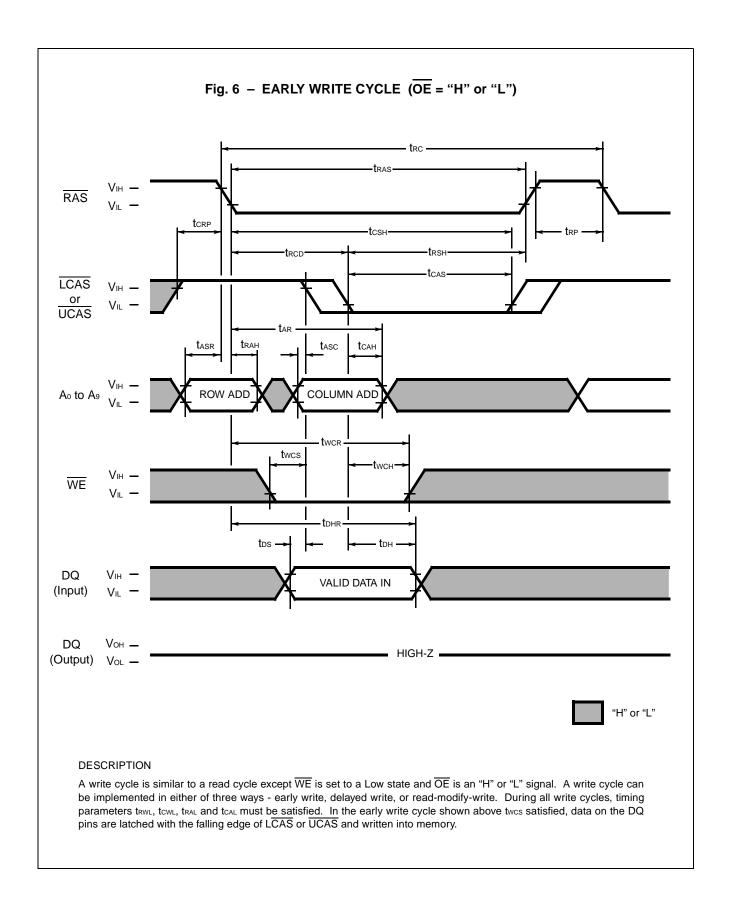

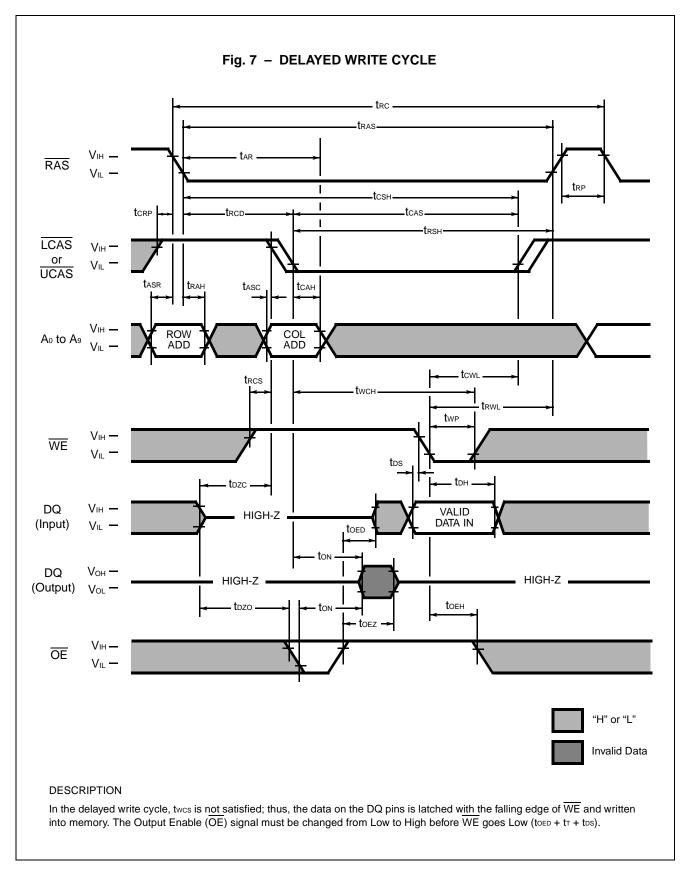

#### WRITE ENABLE

The read or write mode is determined by the logic state of  $\overline{\text{WE}}$ . When  $\overline{\text{WE}}$  is active Low, a write cycle is initiated; when  $\overline{\text{WE}}$  is High, a read cycle is selected. During the read mode, input data is ignored.

#### **DATA INPUT**

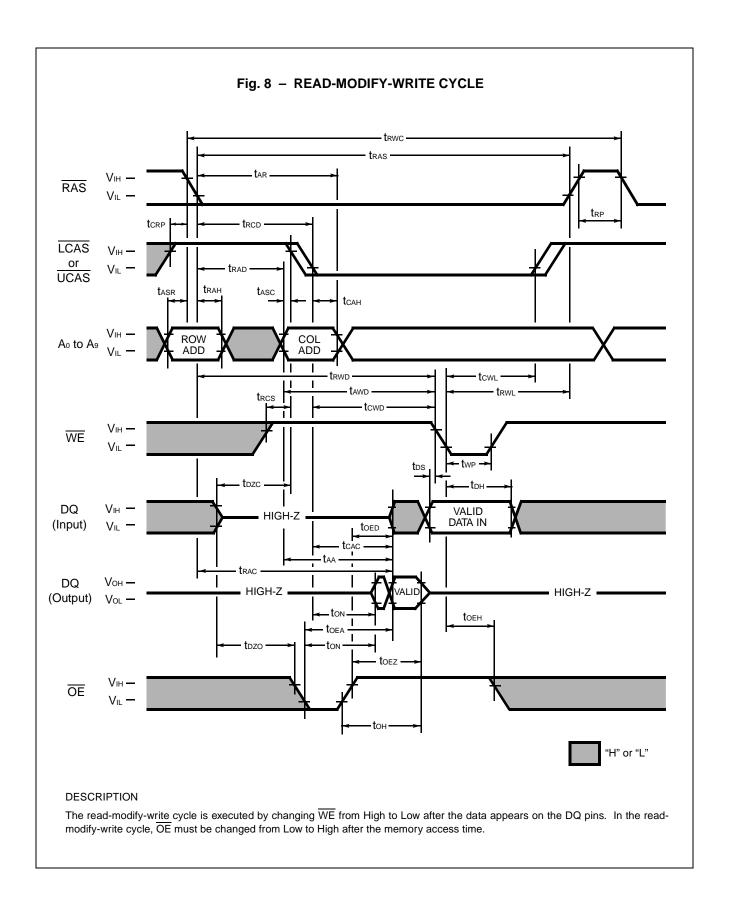

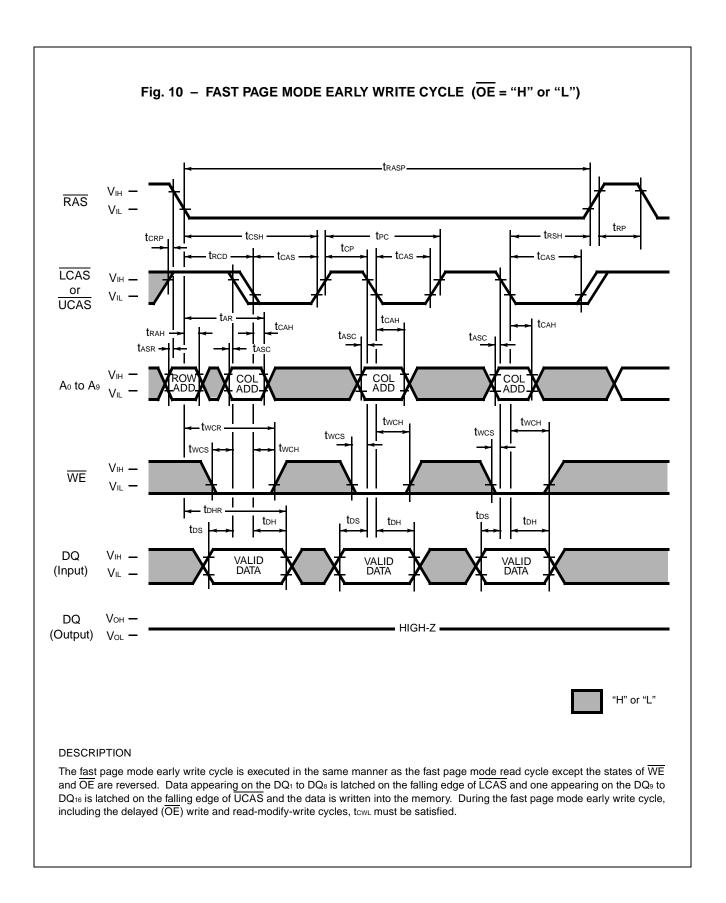

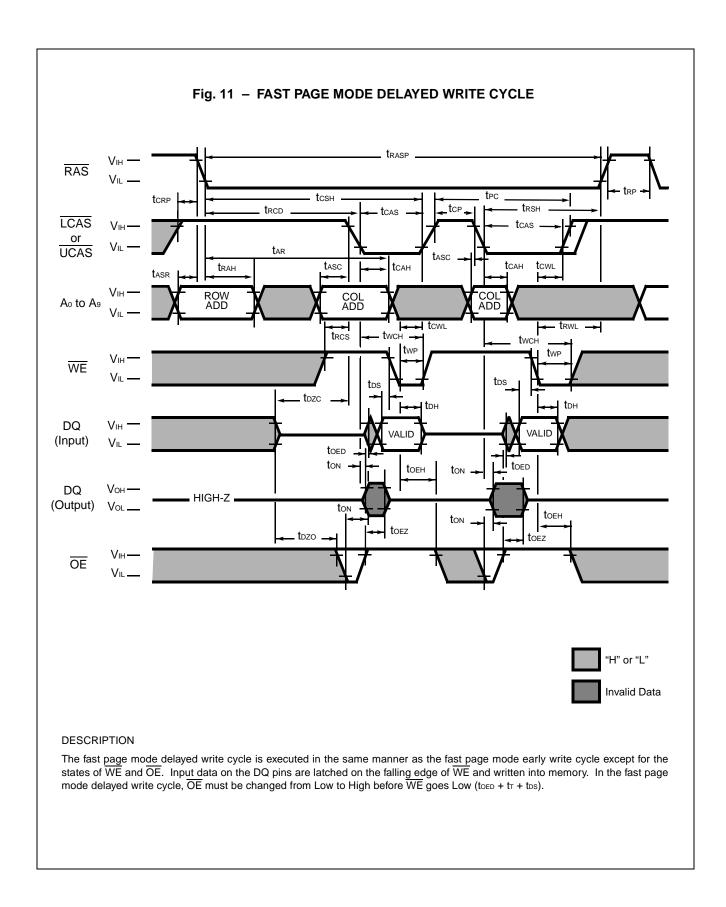

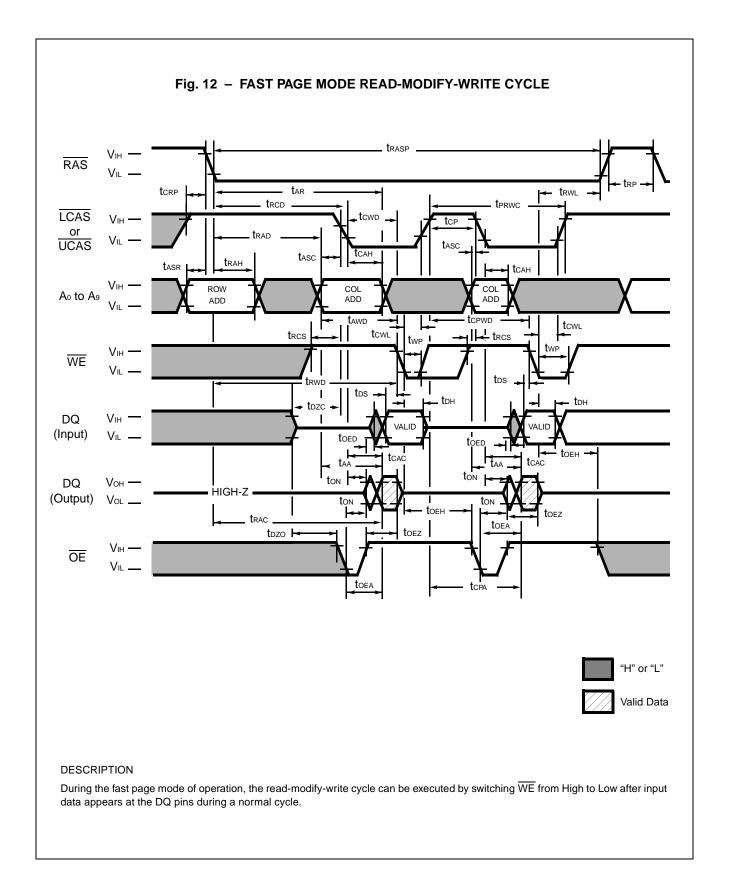

Input data is written into memory in either of three basic ways – an early write cycle, an  $\overline{OE}$  (delayed) write cycle, and a read-modify-write cycle. The falling edge of WE or LCAS / UCAS, whichever is later, serves as the input data-latch strobe. In an early write cycle, the input data of  $\overline{DQ_1}$ - $\overline{DQ_8}$  is strobed by  $\overline{LCAS}$  and  $\overline{DQ_9}$ - $\overline{DQ_{16}}$  is strobed by  $\overline{UCAS}$  and the setup/hold times are referenced to each  $\overline{LCAS}$  and  $\overline{UCAS}$  because  $\overline{WE}$  goes Low before  $\overline{LCAS}$  /  $\overline{UCAS}$ . In a delayed write or a read-modify-write cycle,  $\overline{WE}$  goes Low after  $\overline{LCAS}$  /  $\overline{UCAS}$ ; thus, input data is strobed by  $\overline{WE}$  and all setup/hold times are referenced to the write-enable signal.

#### **DATA OUTPUT**

The three-state buffers are TTL compatible with a fanout of two TTL loads. Polarity of the output data is identical to that of the input; the output buffers remain in the high-impedance state until the column address strobe goes Low. When a read or read-modify-write cycle is executed, valid outputs are obtained under the following conditions:

trac: from the falling edge of RAS when trcd (max.) is satisfied.

tcac: from the falling edge of LCAS (for DQ<sub>1</sub>-DQ<sub>8</sub>) UCAS (for DQ<sub>9</sub>-DQ<sub>16</sub>) when tRCD is greater than tRCD (max.).

taa : from column address input when trad is greater than trad (max.).

toba: from the falling edge of  $\overline{OE}$  when  $\overline{OE}$  is brought Low after trac, toac, or taa, and trop (max.) is satisfied.

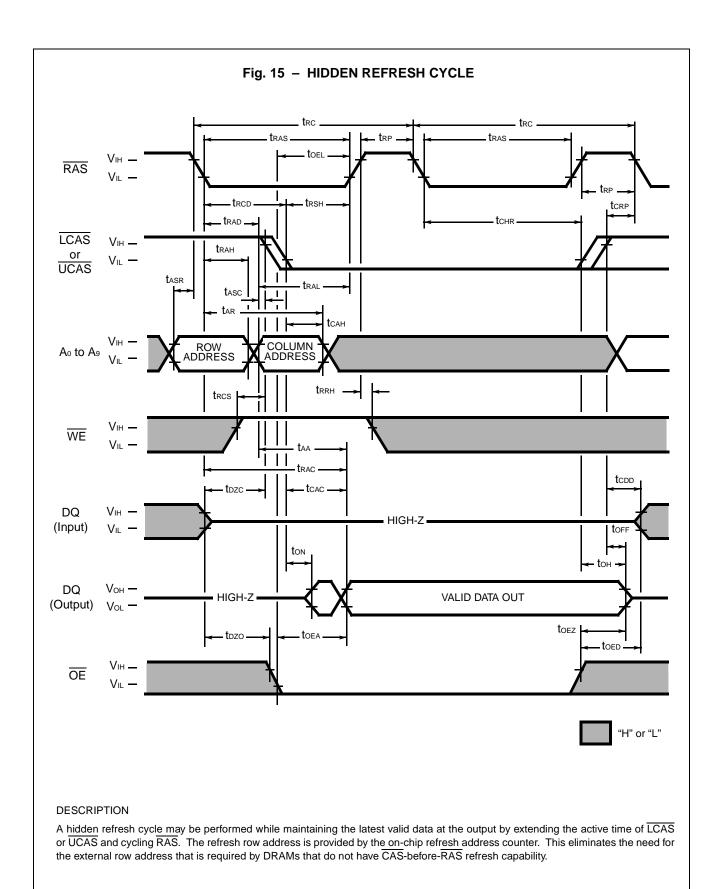

The data remains valid until either  $\overline{LCAS}$  /  $\overline{UCAS}$  or  $\overline{OE}$  returns to a High logic level. When an early write is executed, the output buffers remain in a high-impedance state during the entire cycle.

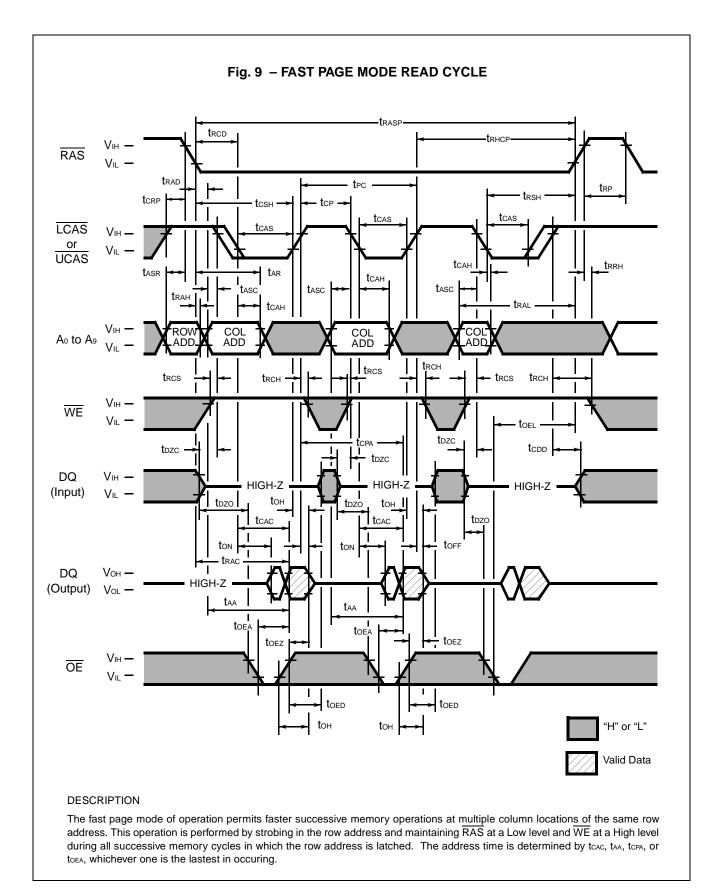

#### **FAST PAGE MODE OF OPERATION**

The fast page mode of operation provides faster memory access and lower power dissipation. The fast page mode is implemented by keeping the same row address and strobing in successive column addresses. To satisfy these conditions,  $\overline{RAS}$  is held Low for all contiguous memory cycles in which row addresses are common. For each fast page of memory, any of 1,024×16-bits can be accessed and, when multiple MB8118160As are used,  $\overline{CAS}$  is decoded to select the desired memory fast page. Fast page mode operations need not be addressed sequentially and combinations of read, write, and/or read-modify-write cycles are permitted.

#### **■ DC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.) Notes 3

|                                  |                |                   |                                                                                                                                                                                                                                                           |      | Value |      |      |  |

|----------------------------------|----------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|--|

| Parameter Notes                  |                | Symbol            | Conditions                                                                                                                                                                                                                                                |      | Value | ı    | Unit |  |

|                                  |                |                   |                                                                                                                                                                                                                                                           | Min. | Тур.  | Max. |      |  |

| Output high voltage              |                | Vон               | Iон = −5.0 mA                                                                                                                                                                                                                                             | 2.4  | _     | _    | V    |  |

| Output low voltage               | 1              | Vol               | IoL = +4.2 mA                                                                                                                                                                                                                                             | _    | _     | 0.4  | V    |  |

| Input leakage currer             | nt (any input) | I <sub>I(L)</sub> | $\begin{array}{l} 0 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{V}_{\text{CC}}; \\ 4.5 \text{ V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{ V}; \\ \text{Vss} = 0 \text{ V}; \text{ All other pins} \\ \text{not under test} = 0 \text{ V} \end{array}$ | -10  | _     | 10   | μΑ   |  |

| Output leakage curre             | ent            | IDO(L)            | 0 V ≤ Voυτ ≤ Vcc;<br>Data out disabled                                                                                                                                                                                                                    | -10  | _     | 10   |      |  |

| Operating current                | MB8118160A-60  |                   | RAS & LCAS, UCAS                                                                                                                                                                                                                                          |      |       | 160  |      |  |

| (Average power supply current) 2 | MB8118160A-70  | Icc <sub>1</sub>  | cycling;<br>trc = min.                                                                                                                                                                                                                                    |      | _     | 150  | mA   |  |

| Standby current                  | TTL level      |                   | $\overline{RAS} = \overline{LCAS}$ , $\overline{UCAS} = V_{IH}$                                                                                                                                                                                           |      |       | 2.0  |      |  |

| (Power supply current) 2         | CMOS level     | Icc2              | $\overline{RAS} = \overline{LCAS}$ , $\overline{UCAS} \ge V_{CC} - 0.2$ V                                                                                                                                                                                 | _    | _     | 1.0  | mA   |  |

| Refresh current#1                | MB8118160A-60  |                   | TCAS, UCAS = VIH, RAS                                                                                                                                                                                                                                     |      |       | 160  |      |  |

| (Average power supply current) 2 | MB8118160A-70  | Іссз              | cycling;<br>trc = min.                                                                                                                                                                                                                                    | _    | _     | 150  | mA   |  |

| Fast Page Mode                   | MB8118160A-60  |                   | $\overline{RAS} = V_{\text{L}}, \overline{LCAS} = \overline{UCAS}$                                                                                                                                                                                        |      |       | 100  |      |  |

| Current 2                        | MB8118160A-70  | ICC4              | Icc4 cycling; — — — tec = min.                                                                                                                                                                                                                            |      | _     | 90   | mA   |  |

| Refresh current#2                | MB8118160A-60  | <u></u>           | <u></u>                                                                                                                                                                                                                                                   |      |       |      | 160  |  |

| (Average power supply current) 2 | MB8118160A-70  | Icc5              | CAS-before-RAS;<br>trc = min.                                                                                                                                                                                                                             | _    | _     | 150  | mA   |  |

| Refresh current#3                | MB8118160A-60  |                   | RAS = VIL, CAS = VIL                                                                                                                                                                                                                                      |      |       | 4000 |      |  |

| (Average power supply current)   | MB8118160A-70  | Icc <sub>9</sub>  | Self refresh;<br>trass = min.                                                                                                                                                                                                                             | _    | _     | 1000 | μА   |  |

#### **■ AC CHARACTERISTICS**

(At recommended operating conditions unless otherwise noted.)

Notes 3, 4, 5

| (At recommended operating conditions unles |                                             |        |              |        |          | Notes  |         |      |

|--------------------------------------------|---------------------------------------------|--------|--------------|--------|----------|--------|---------|------|

| No.                                        | Parameter                                   | Notes  | Symbol       | MB8118 | 3160A-60 | MB8118 | 160A-70 | Unit |

| 140.                                       | i diametei                                  | 140163 | Symbol       | Min.   | Max.     | Min.   | Max.    | Oint |

| 1                                          | Time Between Refresh                        |        | tref         | _      | 16.4     | _      | 16.4    | ms   |

| 2                                          | Random Read/Write Cycle Time                |        | trc          | 110    | _        | 130    | _       | ns   |

| 3                                          | Read-Modify-Write Cycle Time                |        | trwc         | 150    | _        | 174    | _       | ns   |

| 4                                          | Access Time from RAS                        | 6, 9   | trac         | _      | 60       | _      | 70      | ns   |

| 5                                          | Access Time from CAS                        | 7, 9   | <b>t</b> cac | _      | 15       | _      | 17      | ns   |

| 6                                          | Column Address Access Time                  | 8, 9   | <b>t</b> AA  | _      | 30       | _      | 35      | ns   |

| 7                                          | Output Hold Time                            |        | tон          | 3      | _        | 3      | _       | ns   |

| 8                                          | Output Buffer Turn On Delay Time            | )      | ton          | 0      | _        | 0      | _       | ns   |

| 9                                          | Output Buffer Turn off Delay<br>Time        | 10     | toff         | _      | 15       | _      | 17      | ns   |

| 10                                         | Transition Time                             |        | t⊤           | 3      | 50       | 3      | 50      | ns   |

| 11                                         | RAS Precharge Time                          |        | <b>t</b> RP  | 40     | _        | 50     | _       | ns   |

| 12                                         | RAS Pulse Width                             |        | <b>t</b> ras | 60     | 100000   | 70     | 100000  | ns   |

| 13                                         | RAS Hold Time                               |        | <b>t</b> rsh | 15     | _        | 17     | _       | ns   |

| 14                                         | CAS to RAS Precharge Time                   |        | <b>t</b> CRP | 5      | _        | 5      | _       | ns   |

| 15                                         | RAS to CAS Delay Time                       | 11, 12 | trcd         | 20     | 45       | 20     | 53      | ns   |

| 16                                         | CAS Pulse Width                             |        | <b>t</b> cas | 15     | _        | 17     | _       | ns   |

| 17                                         | CAS Hold Time                               |        | <b>t</b> csH | 60     | _        | 70     | _       | ns   |

| 18                                         | CAS Precharge Time (Normal)                 | 19     | <b>t</b> CPN | 10     | _        | 10     | _       | ns   |

| 19                                         | Row Address Set Up Time                     |        | <b>t</b> asr | 0      | _        | 0      | _       | ns   |

| 20                                         | Row Address Hold Time                       |        | <b>t</b> RAH | 10     | _        | 10     | _       | ns   |

| 21                                         | Column Address Set Up Time                  |        | tasc         | 0      | _        | 0      | _       | ns   |

| 22                                         | Column Address Hold Time                    |        | <b>t</b> CAH | 15     | _        | 15     | _       | ns   |

| 23                                         | Column Address Hold Time from               | RAS    | <b>t</b> ar  | 35     | _        | 35     | _       | ns   |

| 24                                         | RAS to Column Address Delay<br>Time         | 13     | tRAD         | 15     | 30       | 15     | 35      | ns   |

| 25                                         | Column Address to RAS Lead Tin              | ne     | <b>t</b> RAL | 30     | _        | 35     | _       | ns   |

| 26                                         | Column Address to CAS Lead Tin              | ne     | <b>t</b> CAL | 30     | _        | 35     | _       | ns   |

| 27                                         | Read Command Set Up Time                    |        | trcs         | 0      | _        | 0      | _       | ns   |

| 28                                         | Read Command Hold Time<br>Referenced to RAS | 14     | <b>t</b> rrh | 0      | _        | 0      | _       | ns   |

| 29                                         | Read Command Hold Time<br>Referenced to CAS | 14     | tксн         | 0      | _        | 0      | _       | ns   |

| 30                                         | Write Command Set Up Time                   | 15, 20 | twcs         | 0      | _        | 0      | _       | ns   |

| 31                                         | Write Command Hold Time                     |        | <b>t</b> wcH | 15     | _        | 15     | _       | ns   |

| 32                                         | Write Hold Time from RAS                    |        | twcr         | 35     | _        | 35     | _       | ns   |

(Continued)

#### (Continued)

| No  | Doromotor Notes                                        | Cymbal        | MB8118 | 3160A-60 | MB8118 | 160A-70 | Unit |

|-----|--------------------------------------------------------|---------------|--------|----------|--------|---------|------|

| No. | Parameter Notes                                        | Symbol        | Min.   | Max.     | Min.   | Max.    | Unit |

| 33  | WE Pulse Width                                         | twp           | 15     | _        | 15     | _       | ns   |

| 34  | Write Command to RAS Lead Time                         | trwL          | 15     | _        | 17     | _       | ns   |

| 35  | Write Command to CAS Lead Time                         | tcwL          | 15     |          | 17     | _       | ns   |

| 36  | DIN Set Up Time                                        | tos           | 0      | _        | 0      | _       | ns   |

| 37  | DIN Hold Time                                          | tон           | 15     | _        | 15     | _       | ns   |

| 38  | Data Hold Time from RAS                                | <b>t</b> DHR  | 35     | _        | 35     | _       | ns   |

| 39  | RAS to WE Delay Time 20                                | <b>t</b> RWD  | 80     | _        | 92     | _       | ns   |

| 40  | CAS to WE Delay Time 20                                | tcwd          | 35     | _        | 39     | _       | ns   |

| 41  | Column Address to WE Delay Time                        | <b>t</b> AWD  | 50     | _        | 57     | _       | ns   |

| 42  | RAS Precharge Time to CAS Active Time (Refresh Cycles) | <b>t</b> RPC  | 5      | _        | 5      | _       | ns   |

| 43  | CAS Set Up Time for CAS-before-RAS Refresh             | tcsr          | 0      | _        | 0      | _       | ns   |

| 44  | CAS Hold Time for CAS-before-RAS Refresh               | tchr          | 10     | _        | 12     | _       | ns   |

| 45  | Access Time from OE 9                                  | <b>t</b> oea  | _      | 15       | _      | 17      | ns   |

| 46  | Output Buffer Turn Off Delay from OE                   | <b>t</b> oez  | _      | 15       | _      | 17      | ns   |

| 47  | OE to RAS Lead Time for Valid Data                     | toel          | 10     | _        | 10     | _       | ns   |

| 48  | OE Hold Time Referenced to WE                          | tоен          | 5      | _        | 5      | _       | ns   |

| 49  | OE to Data in Delay Time                               | toed          | 15     | _        | 17     | _       | ns   |

| 50  | CAS to Data in Delay Time                              | tcdd          | 15     |          | 17     | _       | ns   |

| 51  | DIN to CAS Delay Time 17                               | <b>t</b> DZC  | 0      | _        | 0      | _       | ns   |

| 52  | DIN to OE Delay Time 17                                | <b>t</b> DZO  | 0      | _        | 0      | _       | ns   |

| 60  | Fast Page Mode RAS Pulse Width                         | trasp         | _      | 100000   | _      | 100000  | ns   |

| 61  | Fast Page Mode Read/Write Cycle Time                   | <b>t</b> PC   | 40     | _        | 45     | _       | ns   |

| 62  | Fast Page Mode Read-Modify-Write Cycle Time            | <b>t</b> PRWC | 80     | _        | 89     | _       | ns   |

| 63  | Access Time from CAS Precharge  9, 18                  | <b>t</b> CPA  | _      | 35       | _      | 40      | ns   |

| 64  | Fast Page Mode CAS Precharge Time                      | <b>t</b> CP   | 10     | _        | 10     | _       | ns   |

| 65  | Fast Page Mode RAS Hold Time from CAS Precharge        | <b>t</b> RHCP | 35     | _        | 40     | _       | ns   |

| 66  | Fast Page Mode CAS Precharge to WE Delay Time          | <b>t</b> CPWD | 55     | _        | 62     | _       | ns   |

#### Notes:1. Referenced to Vss.

- 2. lcc depends on the output load conditions and cycle rates; The specified values are obtained with the output open.

- Icc depends on the number of address change as  $\overline{RAS} = V_{IL} \overline{UCAS} = V_{IH}$ ,  $\overline{LCAS} = V_{IH}$  and  $V_{IL} > -0.3V$ . Icc<sub>1</sub>, Icc<sub>3</sub> Icc<sub>4</sub> and Icc<sub>5</sub> are specified at one time of address change during  $\overline{RAS} = V_{IL}$  and  $\overline{UCAS} = V_{IH}$ , Icc<sub>2</sub> is specified during  $\overline{RAS} = V_{IH}$  and  $V_{IL} > -0.3V$ .

- An initial pause (RAS = CAS = V<sub>IH</sub>) of 200μs is required after power-up followed by any eight RAS-only cycles before proper device operation is achieved. In case of using internal refresh counter, a minimum of eight CAS-before-RAS initialization cycles instead of 8 RAS cycles are required.

- 4. AC characteristics assume  $t_T = 5$ ns.

- 5. V<sub>IH</sub> (min.) and V<sub>IL</sub> (max.) are reference levels for measuring timing of input signals. Also transition times are measured between V<sub>IH</sub> (min.) and V<sub>IL</sub> (max.).

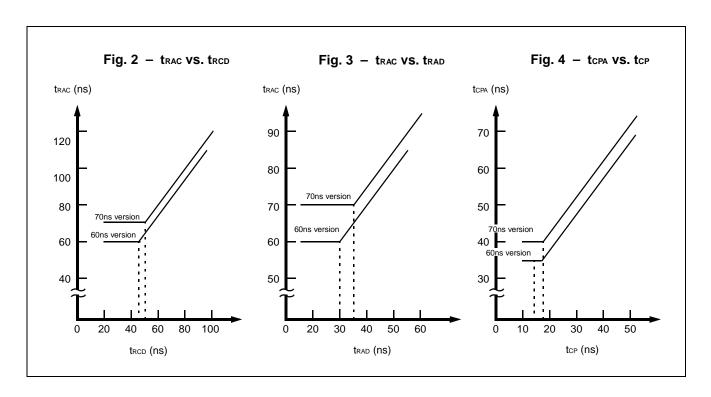

- 6. Assumes that tRCD ≤ tRCD (max.), tRAD ≤ tRAD (max.). If tRCD is greater than the maximum recommended value shown in this table, tRAC will be increased by the amount that tRCD exceeds the value shown. Refer to Fig.2 and 3.

- 7. If  $trcd \ge trcd$  (max.),  $trad \ge trad$  (max.), and  $tasc \ge taa-tcac-t\tau$ , access time is tcac.

- 8. If trad  $\geq$  trad (max.) and tasc  $\leq$  taa-tcac-tt, access time is taa.

- 9. Measured with a load equivalent to two TTL loads and 50pF.

- 10. toff and toez are specified that output buffer change to high impedance state.

- 11. Operation within the trod (max.) limit ensures that trac (max.) can be met. trod (max.) is specified as a reference point only; if trod is greater than the specified trod (max.) limit, access time is controlled exclusively by trac or trad.

- 12.  $t_{RCD}$  (min.) =  $t_{RAH}$  (min.) +  $2t_{T}$  +  $t_{ASC}$  (min.).

- 13. Operation within the trad (max.) limit ensures that trac (max.) can be met. trad (max.) is specified as a reference point only; if trad is greater than the specified trad (max.) limit, access tome is controlled exclusively by trac or trad.

- 14. Either trrh or trch must be satisfied for a read cycle.

- 15. twcs is specified as a reference point only. If twcs ≥ twcs (min.) the data output pin will remain High-Z state through entire cycle.

- 16. Assumes that twcs < twcs (min.).

- 17. Either tozc or tozo must be satisfied.

- 18. tcpa is access time from the selection of a new column address (that is caused by changing both UCAS and LCAS from "L" to "H"). Therefore, if tcp is long, tcpa is longer than tcpa (max.).

- 19. Assumes that CAS-before-RAS refresh.

- 20. twcs, tcwb, trwb, tawb and tcpwb are not restrictive operating parameters. They are included in the data sheet as an electrical characteristic only. If twcs ≥ twcs (min.), the cycle is an early write cycle and Dout pin will maintain high impedance state throughout the entire cycle. If tcwb ≥ tcwb (min.), trwb ≥ trwb (min.), and tawb ≥ tawb (min.), tcpwb ≥ tcpwb (min.), the cycle is a read-modify-write cycle and data from the selected cell will appear at the Dout pin. If neither of the above conditions is satisfied, the cycle is a delayed write cycle and invalid data will appear the Dout pin, and write operation can be executed by satisfying trwb, tcwb, and trab specifications.

#### **■ FUNCTIONAL TRUTH TABLE**

|                                     |     | Clo         | ock In      | put |     | Add   | ress   | lr                  | nput/Ou                  | tput Da             | ta                       |         |                          |

|-------------------------------------|-----|-------------|-------------|-----|-----|-------|--------|---------------------|--------------------------|---------------------|--------------------------|---------|--------------------------|

| Operation<br>Mode                   | RAS | 1046        | UCAS        | WE  | OE  | Row   | Column | DQ₁ t               | o DQ8                    | DQ <sub>9</sub> to  | DQ16                     | Refresh | Note                     |

|                                     | KAS | LCAS        | UCAS        | WE  | OE  | KOW   | Column | Input               | Output                   | Input               | Output                   |         |                          |

| Standby                             | Н   | Н           | Н           | Х   | Х   | _     | _      | _                   | High-Z                   | _                   | High-Z                   | _       |                          |

| Read Cycle                          | L   | L<br>H<br>L | H<br>L<br>L | Н   | L   | Valid | Valid  |                     | Valid<br>High-Z<br>Valid | _                   | High-Z<br>Valid<br>Valid | Yes*    | trcs ≥ trcs<br>(min.)    |

| Write Cycle<br>(Early Write)        | L   | L<br>H<br>L | H<br>L<br>L | L   | Х   | Valid | Valid  | Valid<br>—<br>Valid | High-Z                   | —<br>Valid<br>Valid | High-Z                   | Yes*    | twcs ≥<br>twcs<br>(min.) |

| Read-Modify-<br>Write Cycle         | L   | L<br>H<br>L | H<br>L<br>L | H→L | L→H | Valid | Valid  | Valid<br>—<br>Valid | Valid<br>High-Z<br>Valid | —<br>Valid<br>Valid | High-Z<br>Valid<br>Valid | Yes*    |                          |

| RAS-only<br>Refresh Cycle           | L   | Н           | Н           | Х   | Х   | Valid | _      | _                   | High-Z                   | _                   | High-Z                   | Yes     |                          |

| CAS-before-<br>RAS Refresh<br>Cycle | L   | L           | L           | Х   | Х   | _     | _      | _                   | High-Z                   | _                   | High-Z                   | Yes     | tcsr ≥<br>tcsr<br>(min.) |

| Hidden Refresh<br>Cycle             | H→L | L<br>H<br>L | H<br>L<br>L | Н→Х | L   | _     | _      | _                   | Valid<br>High-Z<br>Valid | _                   | High-Z<br>Valid<br>Valid | Yes     | Previous<br>data is kept |

Note: X; "H" or "L"

<sup>\*;</sup> It is impossible in Hyper Page Mode.

#### **DESCRIPTION**

To implement a read operation, a valid address is latched by the  $\overline{RAS}$  and  $\overline{LCAS}$  or  $\overline{UCAS}$  address strobes and with  $\overline{WE}$  set to a High level and  $\overline{OE}$  set to a low level, the output is valid once the memory access time has elapsed.  $\overline{LCAS}$  controls the input/output data on DQ1 to DQ8 pins,  $\overline{UCAS}$  controls one on DQ8-DQ16 pins. The access time is determined by  $\overline{RAS}$ (trac),  $\overline{LCAS}$ /UCAS(trac),  $\overline{OE}$ (toea) or column addresses (taa) under the following conditions:

If trcd > trcd(max.), access time = tcac.

If  $t_{RAD} > t_{RAD}(max.)$ , access time =  $t_{AA}$ .

If  $\overline{OE}$  is brought Low after trac, tcac, or taa(whichever occurs later), access time = toea.

However, if either LCAS/UCAS or OE goes High, the output returns to a high-impedance state after ton is satisfied.

#### **DESCRIPTION**

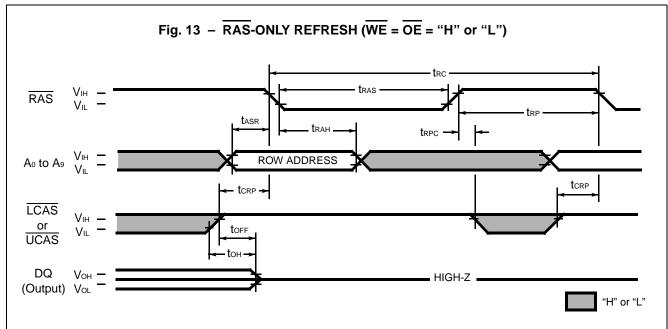

Refresh of RAM memory cells is accomplished by performing a read, a <u>write</u>, or a read-mo<u>dify</u>-write cycle at each of 1,024 row addresses every 16.4-milliseconds. Three refresh modes are available: RAS-only refresh, CAS-before-RAS refresh, and hidden refresh.

RAS-only refresh is performed by keeping RAS Low and LCAS and UCAS High throughout the cycle; the row address to be refreshed is latched on the falling edge of RAS. During RAS-only refresh, DQ pins are kept in a high-impedance state.

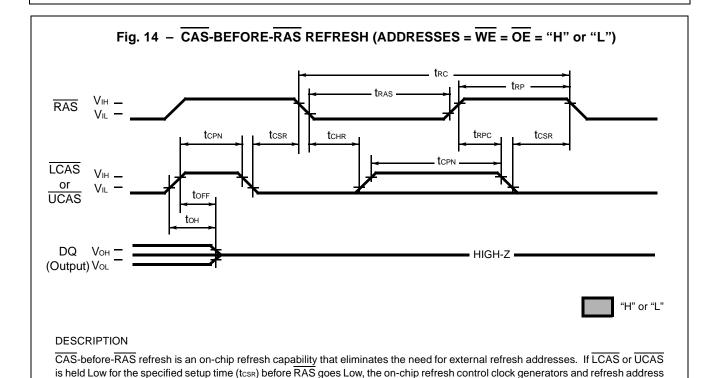

counter are enabled. An internal refresh operation automatically occurs and the refresh address counter is internally incremented

in preparation for the next  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  refresh operation.

#### DESCRIPTION

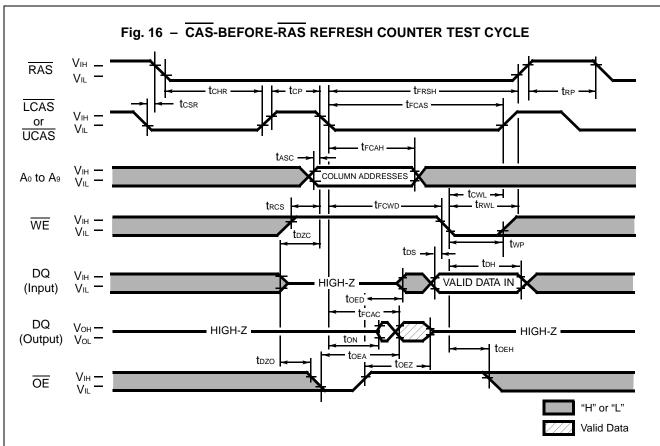

A special timing sequence using the  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  refresh counter test cycle provides a convenient method to verify the function of  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  refresh circuitry. If a  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  refresh cycle  $\overline{\text{CAS}}$  makes a transition from High to Low while  $\overline{\text{RAS}}$  is held Low, read and write operations are enabled as shown above. Row and column addresses are defined as follows:

Row Address: Bits  $A_0$  through  $A_9$  are defined by the on-chip refresh counter.

Column Addresses: Bits A<sub>0</sub> through A<sub>9</sub> are defined by latching levels on A<sub>0</sub>-A<sub>9</sub> at the second falling edge of CAS.

The CAS-before-RAS Counter Test procedure is as follows;

- 1) Initialize the internal refresh address counter by using 8 RAS-only refresh cycles.

- 2) Use the same column address throughout the test.

- 3) Write "0" to all 1,024 row addresses at the same column address by using normal write cycles.

- 4) Read "0" written in procedure 3) and check; simultaneously write "1" to the same addresses by using CAS-before-RAS refresh counter test (read-modify-write cycles). Repeat this procedure 1,024 times with addresses generated by the internal refresh address counter.

- 5) Read and check data written in procedure 4) by using normal read cycle for all 1,024 memory locations.

- 6) Reverse test data and repeat procedures 3), 4), and 5).

#### (At recommended operating conditions unless otherwise noted.)

| No. | Parameter                | Cumbal        | MB8118 | 160A-60 | MB8118 | Unit |       |

|-----|--------------------------|---------------|--------|---------|--------|------|-------|

| NO. | Parameter                | Symbol        | Min.   | Max.    | Min.   | Max. | Ollic |

| 90  | Access Time from CAS     | <b>t</b> FCAC |        | 50      | ı      | 55   | ns    |

| 91  | Column Address Hold Time | <b>t</b> FCAH | 35     | _       | 35     | _    | ns    |

| 92  | CAS to WE Delay Time     | trcwd         | 70     | _       | 77     | _    | ns    |

| 93  | CAS Pulse width          | <b>t</b> FCAS | 90     | _       | 99     | _    | ns    |

| 94  | RAS Hold Time            | <b>t</b> FRSH | 90     | _       | 99     | _    | ns    |

Note: Assumes that CAS-before-RAS refresh counter test cycle only.

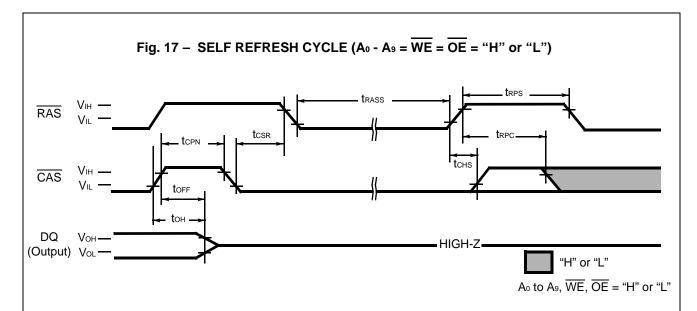

(At recommended operating conditions unless otherwise noted.)

| No. Parame | Parameter          | Symbol       | Symbol MB8118160A-60 |      | MB8118 | Unit |       |

|------------|--------------------|--------------|----------------------|------|--------|------|-------|

| 140.       | Faranietei         | Syllibol     | Min.                 | Max. | Min.   | Max. | Oiiit |

| 100        | RAS Pulse Width    | trass        | 100                  |      | 100    | I    | μs    |

| 101        | RAS Precharge Time | <b>t</b> RPS | 110                  |      | 125    | _    | ns    |

| 102        | CAS Hold Time      | <b>t</b> chs | -50                  |      | -50    |      | ns    |

Note: Assumes self refresh cycle only.

#### DESCRIPTION

The self refresh cycle provides a refresh operation without external clock and external Address. Self refresh control circuit on chip is operated in the self refresh cycle and refresh operation can be automatically executed using internal refresh address counter and timing generator.

If  $\overline{\text{CAS}}$  goes to "L" before  $\overline{\text{RAS}}$  goes to "L" (CBR) and the condition of  $\overline{\text{CAS}}$  "L" and  $\overline{\text{RAS}}$  "L" is kept for term of trass (more than 100µs), the device can enter the self refresh cycle. Following that, refresh operation is automatically executed at fixed intervals using internal refresh address counter during " $\overline{\text{RAS}}$ =L" and " $\overline{\text{CAS}}$ =L".

Exit from self refresh cycle is performed by toggling RAS and CAS to "H" with specified tCHS min. In this time, RAS must be kept "H" with specified tRPS min.

Using self refresh mode, data can be retained without external CAS signal during system is in standby.

#### Restriction for Self Refresh operation;

For self refresh operation, the notice below must be considered.

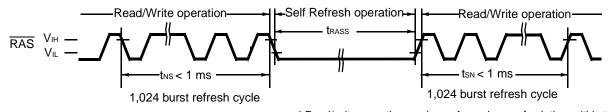

- In the case that distributed CBR refresh are operated between read/write cycles

Self refresh cycles can be executed without special rule if 1,024 cycles of distributed CBR refresh are executed within tree max.

- 2) In the case that burst CBR refresh or distributed/burst  $\overline{RAS}$  only refresh are operated between read/write cycles 1,024 times of burst CBR refresh or 1,024 times of burst  $\overline{RAS}$  only refresh must be executed before and after Self refresh cycles.

$^{\star}$  Read/write operation can be performed non refresh time within this or tsn.

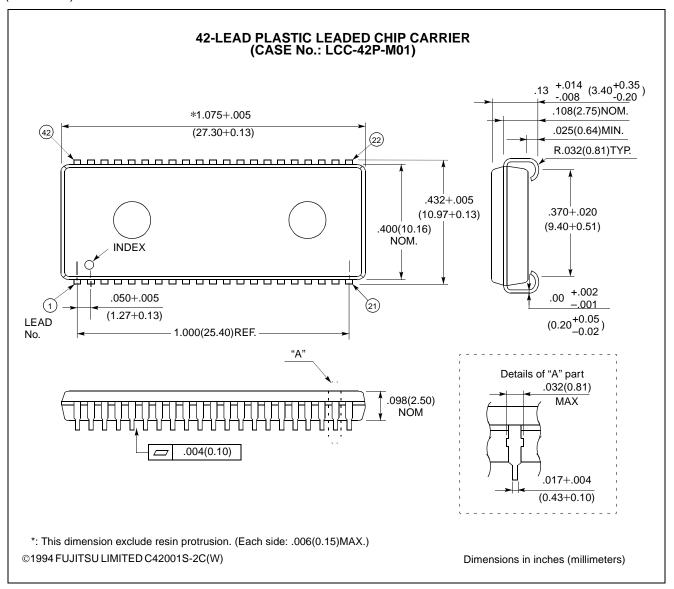

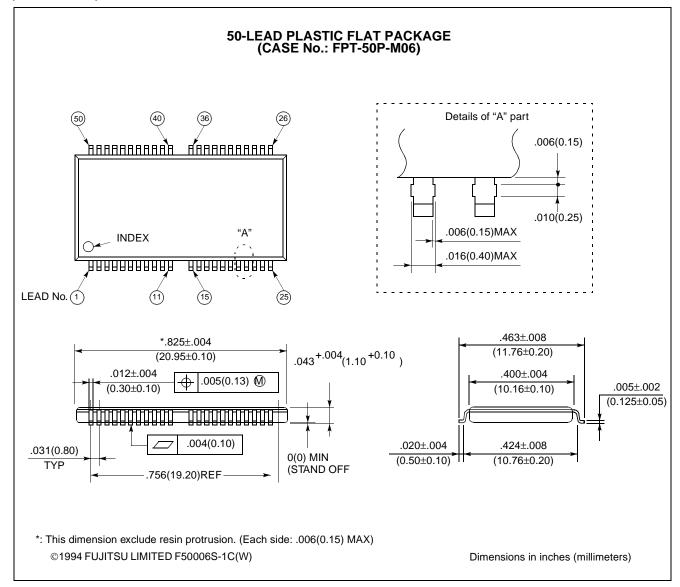

#### **■ PACKAGE DIMENSIONS**

(Suffix: -PJ)

(Continued) (Suffix: -PFTN)

# **FUJITSU LIMITED**

For further information please contact:

#### **Japan**

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices KAWASAKI PLANT, 4-1-1, Kamikodanaka Nakahara-ku, Kawasaki-shi Kanagawa 211-88, Japan Tel: (044) 754-3753

Fax: (044) 754-3332

#### **North and South America**

FUJITSU MICROELECTRONICS, INC. Semiconductor Division 3545 North First Street San Jose, CA 95134-1804, U.S.A.

Tel: (408) 922-9000 Fax: (408) 432-9044/9045

#### Europe

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10 63303 Dreieich-Buchschlag Germany

Tel: (06103) 690-0 Fax: (06103) 690-122

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LIMITED No. 51 Bras Basah Road, Plaza By The Park, #06-04 to #06-07 Singapore 189554

Tel: 336-1600 Fax: 336-1609

#### All Rights Reserved.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical semiconductor applications. Complete information sufficient for construction purposes is not necessarily given.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu assumes no responsibility for inaccuracies.

The information contained in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu.

Fujitsu reserves the right to change products or specifications without notice.

No part of this publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu.

The information contained in this document are not intended for use with equipments which require extremely high reliability such as aerospace equipments, undersea repeaters, nuclear control systems or medical equipments for life support.

#### F9607

© FUJITSU LIMITED Printed in Japan